以前のリビジョンの文書です

公開講座

10時間で学ぶFPGA設計

―Verilog HDLによる電子オルゴール設計を題材に―

はじめに

この講座は,10時間でFPGA設計の基礎を学ぶことを目的としています. わずかな時間で,設計ツールを用いながら,回路を実際にFPGAに 書き込んで動作させます. 最終的には,電子オルガンと電子オルゴールをハードウェア記述言語で 設計します.

ハードウェアの仕様を記述する言語としてVerilogHDLを用います. 特に基礎的な構文だけ用いるので,VerilogHDLの古い標準であるVerilog-95 に準拠します. もちろん,Verilog2001などの新しい標準規格にも,そのまま使うことができます.

このテキストで学ぶにあたり,FPGAやハードウェア記述言語についての 知識は必要ありません. ただし,

- C言語のプログラミングの基礎

- 例えば,式の書き方,代入文やif文の意味

- デジタル回路設計の基礎

- AND,OR,NOTなどの基本ゲート,基本ゲートを用いた組合せ回路,フリップフロップなどの記憶素子

を知っていることを前提とします. ハードウェア記述言語VerilogHDLによるハードウェア設計は, 通常のプログラミング言語によるソフトウェア設計に似ています. VerilogHDLはC言語と構文が似ており,本講座を理解するためには, C言語のごく基礎的な知識が必要です. また,基本ゲートやそれを用いた組合せ回路の動作などのデジタル回路設計の 基礎も知っている必要があります.

日時

- 平成21年8月28日(金)~29日(土)

- ??:00~??:00(両日とも)

会場

- 東広島市

定員

- 名

受講料

申込期間

申込方法

連絡先

受講時に必要なもの

- Xilinx ISE WebPACKをインストールしたノートPC

- Xilinx ISE WebPACKはXilinx社より無償で提供されているFPGA設計ツール

- インストール方法については下記のISE WebPACKのインストールを参照

- 筆記用具

ISE WebPACKのインストール方法

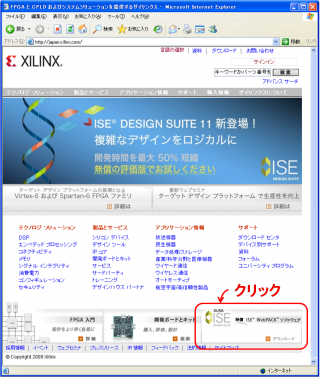

- Xilinx社ホームページにアクセス

- 無償ISE WebPACKをクリックしてダウンロードのページへ

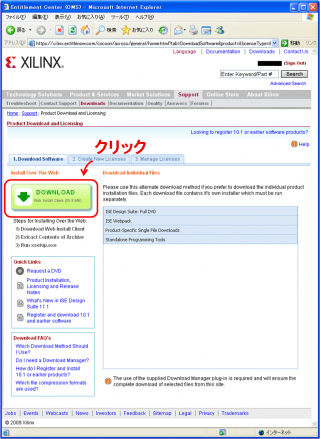

- Web Install Clientをダウンロード

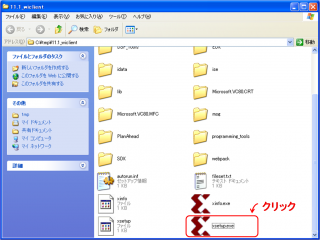

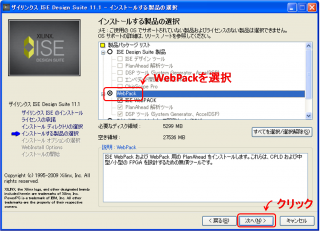

- ファイルを解凍してxsetup.exeを実行し、指示に従いインストール

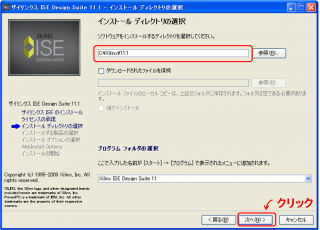

- インストール時の注意点

- インストール先のディレクトリに全角文字やスペースが含まれないようにする

- インストールする製品の選択で「ISE WebPack」を選択

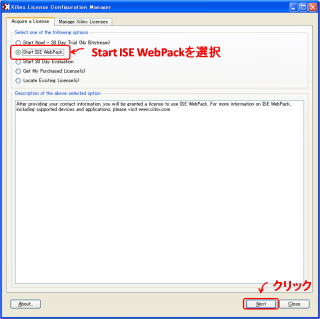

- Xilinx License Configuration Managerで「Start ISE WebPack」を選択